win10 jungo windriver |

您所在的位置:网站首页 › wind river安装步骤 › win10 jungo windriver |

win10 jungo windriver

|

目录 前言 1、安装windriver 1.1、disable Secure Boot 1.2、digital driver signing enforcement 2、FPGA 逻辑下载及PCIE驱动安装 2、PCIE PIO通信测试 3、PCIE DMA通信测试 3.1、vs打开BMD工程 3.2、流程演示 3.3、VS2015 PCIE DMA驱动调试程序 3.4、DMA板卡测试流程 总结 前言 声明:本文仅适用于学习交流!本文使用的软件平台,请支持正版软件。 本文从FPGA硬件工程师的角度进行测试与记录。 相关博客参考: 五、Xilinx PCIE CORE学习; 六、Xilinx PCIE DMA--Sparten6/Kintex-7 BMD 七、Xilinx PCIE DMA 仿真环境搭建 八、win10 jungo windriver

PC系统:win10 教育版 1809 电脑主板:华硕 FPGA工程:SPARTEN6 (基于xapp1052修改) visual_studio:2015。 jungo windriver:v14.3.0 x86_64 (本文使用的是30天试用版,试用不收费。30天过后会收费) jungo windriver下载网址:http://www.jungo.com/st/products/windriver/thank-you/ 1、安装windriver 安装jungo windriver遇到的问题如下图所示:

主要问题为两个: (1)电脑被Secure Boot保护,需要disable Secure Boot。 (2)digital driver signing enforcement。 1.1、disable Secure Boot 首先,确定自己电脑厂家或主板厂家。我的电脑主板是华硕,以华硕为例。其他厂家稍有不同。 详细步骤: (1)重启电脑,开机按【F2】或【DEL】进去BIOS设置界面。 (2)在顶部菜单栏,点击进入【启动】。 (3)选择【快速启动】,将其设置为【disabled】状态。 (4)点击进入【安全启动菜单】,将【操作系统类型】从原来的windows更改为【其他操作系统】 (5)点击进入【密钥管理】,点击【清除安全启动密钥】,确认清除。 (6)返回安全启动菜单,此时【安全启动状态】即secure boot已关闭。保存设置,退出即可。 1.2、digital driver signing enforcement 打开win10 的设置,进入“更新和安全”---恢复----“高级启动”下面的“立即重新启动”,会进入一个重启界面,选择一个选项:“疑难解答”,接着选择“高级选项”,然后选择“查看更多恢复选项”,选择“启动设置”,点击重启,选择“禁用驱动程序强制签名”(就是按数字键7) 若遇到其他Windrive报的错误(具体错误忘记录了),可尝试将下面Base Class设置为Memory controller试试。

2、FPGA 逻辑下载及PCIE驱动安装 测试流程: (1)下载FPGA程序(bit/mcs); (2)打开windriver,按照下图产生PCIE驱动;

(3)按照下图所示勾选;

(3)打开设备管理器,更新PCIE驱动,选择刚才windrive生成的PCIE驱动即可。 (4)win10系统禁用系统签名:更新--恢复--高级启动--立即重新启动--(后续步骤参考百度百科) (5)电脑自动开启重启后,可以进行PIO测试和BMD测试。

2、PCIE PIO通信测试 FPGA测试工程,可以使用PCIE IP自带的example工程即可,添加好对应的约束。 如果自己基于xapp1052搭建的BMD工程,想对其测试PIO操作的话,也可以参考。 测试流程: (1)下载FPGA程序(bit/mcs)。若程序下载好,请跳过此步骤。 (2)关机重启,电脑重启过程中对PCIE IP执行复位动作/并分配相应的地址。若程序下载好,请跳过此步骤。 (3)使用chipscope下载cdc观察文件。步骤:file--import--**.cdc,选择对应的cdc文件。下载mcs和bit效果一样,开机后都需要下载cdc文件,用于chipscope观察波形。(mcs文件需要板卡断电,bit需要关机重启) (4)打开windrive,PIO读写 PCIE,chipscope触发观察波形。

图文步骤: 首先,自己基于xapp1052搭建的BMD工程,需要对其进行modelsim PIO仿真通过,以确定该BMD工程的完整性。 之后,打开windrive

在generate pcie IP时,有设置相应的BAR空间,下图可以看到对应的BAR空间以及地址范围。 若进行与modelsim仿真一样的PIO测试,点击read/write memory,offset 值要设置为0x10,因为modelsim进行PIO仿真时,读写测试地址也是该地址。 从下面的测试结果可知,若offset不是0x10,则回读的数据不是写下去的数值。

3、PCIE DMA通信测试 软件版本: windrive:v14.3.0 x86_64 visual_studio:2015。 FPGA工程:SPARTEN6 (基于xapp1052修改) 3.1、vs打开BMD工程使用visual_studio2015打开windrive目录下的\xilinx\bmd_design\amd64\msdev_2015。(注意VS版本要与BMD程序版本一致) 可见vs工程目录如下图所示。

工程文件介绍(): 文件功能bmd_diag.cBMD测试主文件:用亍用户诊断和调试PCIe的DMA,PCIe的IO寄存器读写,配置空间信息的访问,以及DMA的读写等等。用户可以通过选择需要调试的选项进行FPGA PCIE的调试。bmd_lib.cBMD测试库:bmd_diag.c相关的库凼数diag_lib.c公共库:主要负责调试过程中调试信息的输入输出pci_diag_lib.c公共库:主要负责打印PCI卡的信息以及PCI的配置寄存器信息print_struct.c公共库:提供打印用户当前选择的PCI卡信息的相关函数wdc_diag_lib.c公共库:主要是为用户提供WDC的相关底局驱劢凼数3.2、流程演示 下图仅是参考。注意下图的vendor ID和Device ID。

(1)打开工程后,F5进入测试

(2)根据提示,依次输入: 2,回车 vendor ID值,回车。(该数值来自PCIE IP CORE生成过程中的配置,根据自己PCIE IP实际值输入) Device ID值,回车。(该数值来自PCIE IP CORE生成过程中的配置,根据自己PCIE IP实际值输入) 7,回车。(7,是进行DMA读写测试)

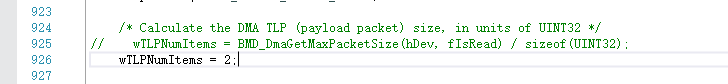

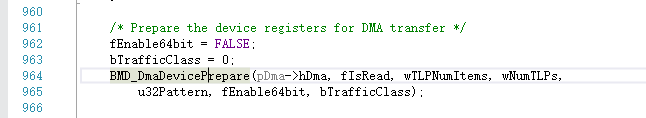

(3)设置的DMA TLP COUNT 注意下图中设置的DMA TLP COUNT =1,之后需要对比chipscope的波形。

配置DMA传输寄存器:TLP SIZE=2 ; TLP COUNT=1 ; TLP PATTERN=12345678 首先,传输方向:TO DEVICE,将数据从PC传输给PCIE 板块,并将数据存储在缓存BRAM中;BRAM写使能、写地址、写数据,trn_rx_data、trn_rx_sof、trn_rx_eof如下图所示: 首先,VS驱动配置DMA传输寄存器,之后PC发送START标志(也是通过PIO方式发送)给PCIE板卡,如RX接收模块时序下图所示;PCIE 板卡接受到START标志之后,PCIE板卡发送MRD请求事务给PC;PC接受到PCIE 板卡的WRD事务后,会响应该请求,将PC中的数据以CPLD报文的形式发送给PCIE板卡,时序如下图所示。通过上面步骤,实现PC将数据传输给PCIE板卡,即 TO DEVICE。

之后,传输方向:FROM DEVICE,将数据从PCIE 板卡 传输给PC,将缓存中的数据读出、发送给PC;BRAM写使能、写地址、写数据,trn_tx_data、trn_tx_sof、trn_tx_eof如下图所示: 首先,VS驱动配置DMA传输寄存器,之后PC发送START标志(也是通过PIO方式发送)给PCIE板卡,如RX接收模块时序下图所示;之后,PCIE 板卡TX发送模块读出缓存数据,并将数据通过MWR事务发给PC。通过上面步骤,PCIE板卡将数据传输给PC,即FROM DEVICE。

总结 本次是以SPARTEN6芯片、基于XAPP1052搭建的工程,传输数据位宽trn_rd/trn_td位宽是32位。使用windrive提供的PCIE驱动,测试了BMD工程的PIO读写访问、DMA读写访问,使用chipscope抓取TLP包。 FPGA的话,需要进一步考虑提高传输速度。同时考虑传输数据位宽是 64/128的时候该如何搭建BMD工程。

|

【本文地址】

今日新闻 |

推荐新闻 |